英特尔在日本VLSI研讨会上展示了即将推出的Intel 18A工艺的详细情况,该工艺节点将取代Intel 3节点,提供更好的时钟和电压调节,计划于2025年下半年进入大规模生产,预计Panther Lake客户端处理器以及Clearwater Forest至强处理器将会采用该工艺节点。

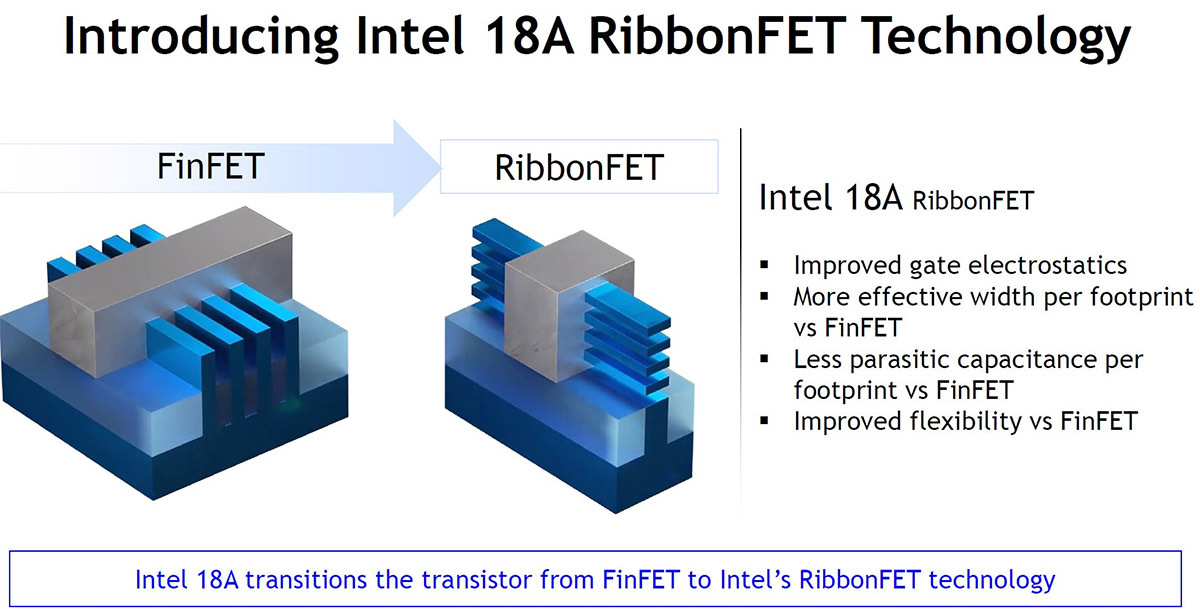

Intel 18A工艺节点结合了RibbonFET(GAA环绕栅极晶体管)和PowerVia(背面电源传输),从而形成全新的金属堆叠架构。RibbonFET采用改进的栅极静电特性,相对于FinFET单位面积有效宽度更大、单位面积寄生电容更小,并且有更好的灵活性。

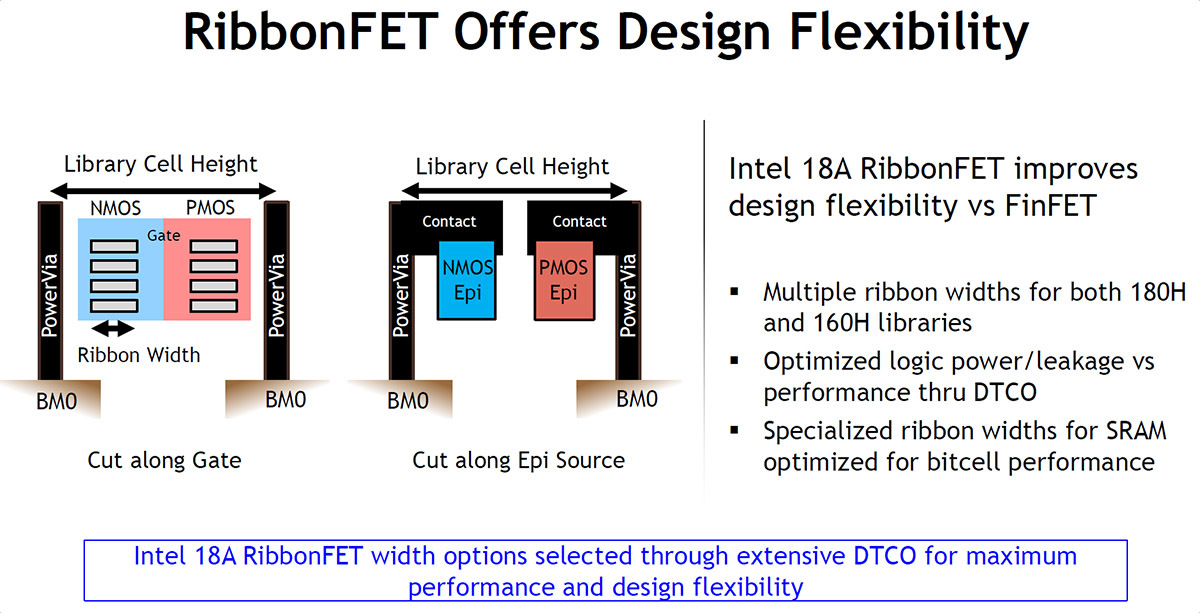

Intel还在RibbonFET上改进了灵活性设计,较原本的FinFET更优秀,为180H和160H库引入了多种带状宽度,透过DTCO优化逻辑功耗、漏电与性能,并为SRAM设计了专门优化的带状宽度以优化位单元性能,所有这些都增强了Intel 18A制程上制造的下一代芯片的性能和设计能力。

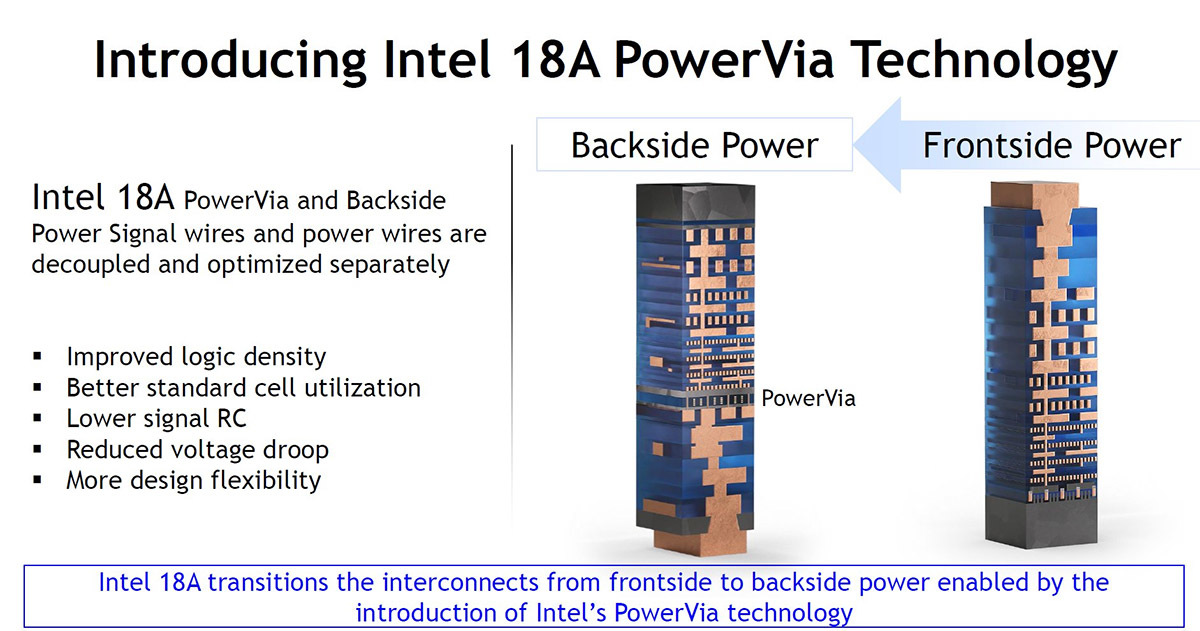

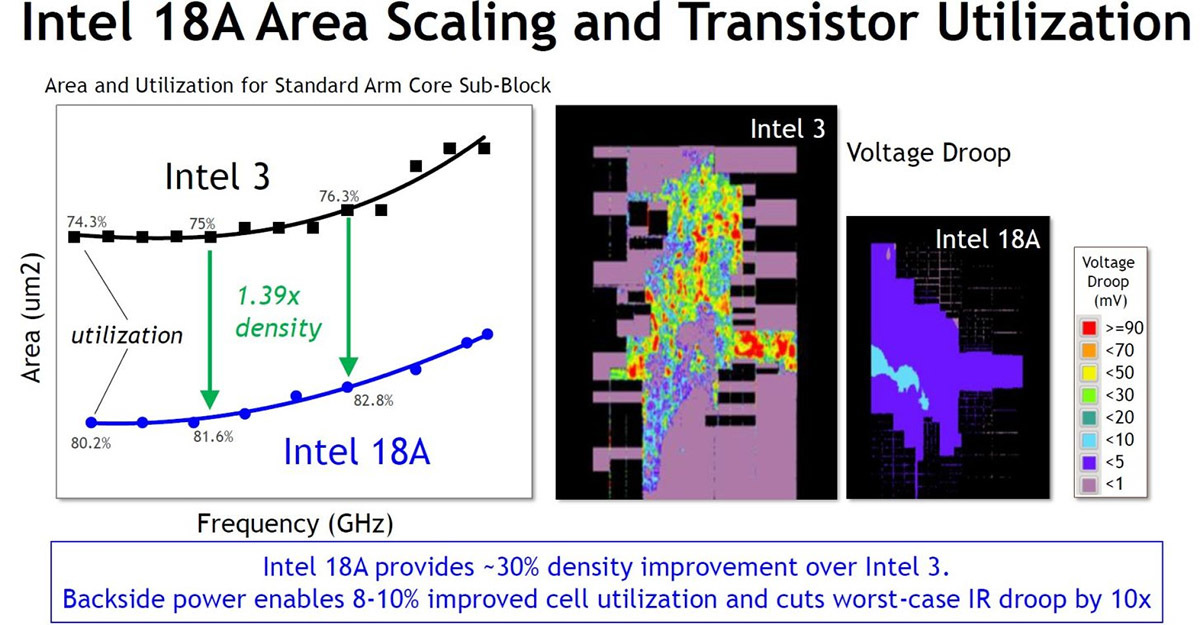

Intel 18A所使用的PowerVia技术也将有助于改善下一代晶体管的功率传输,改技术采用背面电源信号线而非正面电源信号线。这线新线路被分离并分别进行最佳化,从而实现更高的逻辑密度、更好的标准单元利用率、更低的信号RC、减少电压降并提高设计弹性。

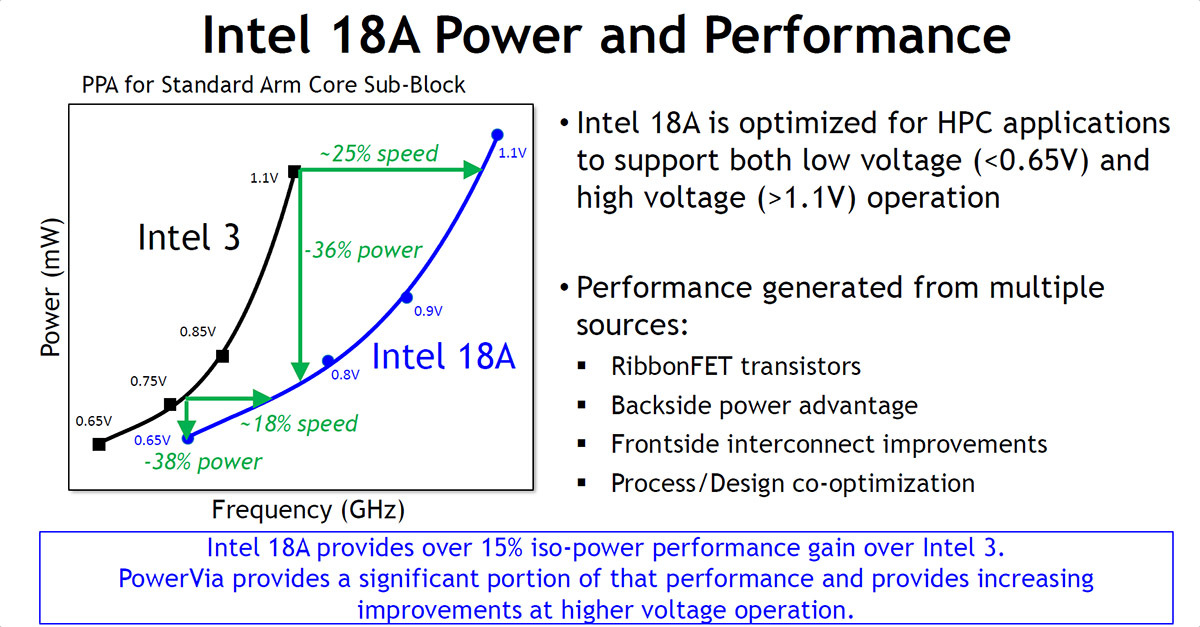

透过这些改进,在同功率下Intel 18A将比Intel 3提供至少15%的性能提升。同样是1.1V电压下,Intel 18A可提供比Intel 3工艺高出25%的频率,并且还支持低于0.65V的低电压下运行,在同频率下可降低38%的功耗。

在提升晶体管密度方面,Intel 18A通过背面供电技术,在电源利用率上提升了8~10%,并将最坏情况下的IR压降减少到原来的1/10。

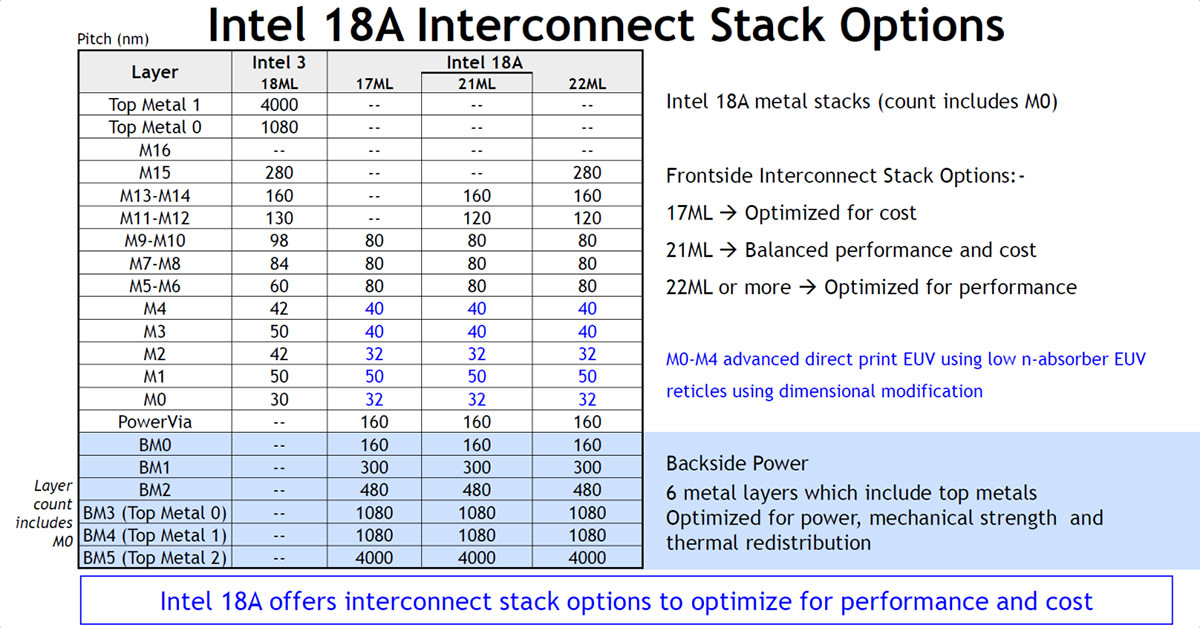

与Intel 3相比,Intel 18A的单元高度在使用高性能设计时从240nm降低至180nm,采用高密度设计则从210nm降低至160mm,而M0/M2间距从30/42nm变成了32/32nm,正面金属层数从Intel 3的12~19层减少到11~16层,并增加了三个背面金属层以支持PowerVia。

M1至M10层的间距已从60nm缩小至32nm,之后在上层再次放宽。M0至M 层采用低数值孔径EUV曝光技术,将所需光罩数量减少了44%,并简化了制造流程。

最后在SRAM扩展方面,Intel 18A的HCC SCRAM密度较Intel 3提升了30%,提供HCC 0.0230um2和HDC 0.0210um2 SRAM。此外Intel 18A工艺并不会止步于此,他们还有更多的制程升级,包括18A-P和18A-PT,将在Direct Connect 2025上发布,并计划在2026至2028年间推出,Intel也希望客户利用这些制程进行芯片生产。

免责声明:本网信息来自于互联网,目的在于传递更多信息,并不代表本网赞同其观点。其内容真实性、完整性不作任何保证或承诺。由用户投稿,经过编辑审核收录,不代表头部财经观点和立场。

证券投资市场有风险,投资需谨慎!请勿添加文章的手机号码、公众号等信息,谨防上当受骗!如若本网有任何内容侵犯您的权益,请及时联系我们。

相关文章

-

花249元给娃娃买件小裙子 Labubu撬动“娃衣”消费

2025-06-2010阅读

-

“618”期间,广东人最爱分期免息?把“能赚会算”坐实了!

2025-06-2010阅读

-

京东家电暗藏"李鬼",杂牌空调冒充“格力“”美的”低价引诱消费者

2025-06-2010阅读

-

李佳琦直播间618收官:六成销量为国货,多品类增长超25%

2025-06-2010阅读

-

公务消费政策收紧,“禁酒令”激活口粮酒市场生机

2025-06-2010阅读

-

新银发经济引领消费升级 携程老友会为银发旅游市场注入新动能

2025-06-2010阅读

-

为什么要转型为消费驱动型社会?

2025-06-2010阅读

-

第四届成渝美食工业博览会在重庆举行

2025-06-2010阅读

-

德州仪器将投资600多亿美元新建7座晶圆厂 为苹果、英伟达等供货

2025-06-2010阅读

-

机器人界“小腰精”星动Q5出道!星动纪元重新定义服务机器人

2025-06-2010阅读